数ある半導体材料の中でも、圧倒的な採用実績を誇るのが「シリコン(Silicon)」です。CPUやメモリ、センサー、ロジック回路など、私たちの身の回りにある多くの電子機器は、シリコンをベースに設計されています。豊富な資源量、優れた結晶構造、加工のしやすさに加え、安定した電気特性を備えていることから、シリコンはまさに半導体の主役といえる存在です。

本記事では、シリコンがなぜここまで広く使われているのかという背景に加え、精製・結晶生成・ウエハー加工の工程、さらにN型・P型半導体の形成メカニズムまで、基礎から体系的に解説します。シリコン材料の理解は、製品開発や調達、品質管理に関わるすべての業務において、有効な技術基盤となるでしょう。

シリコンはなぜ「半導体の主役」なのか?

半導体材料には多くの選択肢があるなかで、最も広く利用され、業界標準として定着しているのがシリコン(Silicon)です。ガリウム砒素や窒化ガリウムなど高性能な化合物半導体が注目を集める場面もありますが、依然としてシリコンの存在感は圧倒的です。では、なぜシリコンがこれほどまでに支持され続けているのでしょうか。その答えは、物理特性・加工性・資源の豊富さ・コストバランスなど、複数の要素が絶妙に融合している点にあります。

このセクションでは、シリコンという素材が「半導体の主役」と呼ばれる理由を、元素の構造や結晶性、産業面の優位性とともに紐解いていきます。

半導体材料の中で圧倒的なシェアを誇る素材

数ある半導体材料の中で、最も広く使われているのがシリコン(Silicon)です。無機系半導体にはさまざまな種類がありますが、なかでもシリコンはコスト、性能、加工性、安定性のバランスに優れ、CPUやメモリ、各種ロジックICなど、幅広いデバイスの基盤となっています。

元素記号Si、原子番号14のシリコンは、「周期表14族」に分類される元素で、最外殻に4つの価電子を持つのが特徴です。このため、他の原子と4本の共有結合を形成できるという性質を持ち、結晶構造を安定的に構成することが可能です。

また、シリコンは地球上に非常に多く存在する元素でもあります。酸素に次いで地殻中に多く含まれ、主に酸化ケイ素(SiO₂)=石英や珪石という形で天然に存在しています。

なぜ日本ではシリコンを「製造」できないのか

豊富な資源であるにもかかわらず、日本国内でシリコン原料を製造する企業は限定的です。その理由は、シリコンの抽出工程に大量の電力が必要となることにあります。

酸化ケイ素からシリコンを取り出すには、還元反応を起こすために高温の電気炉が必要です。この際に消費される電力コストが非常に高いため、「シリコンは電気の缶詰」とも呼ばれるほどです。日本の電気料金では製造コストが合わず、中国、アメリカ、ロシア、ブラジル、フランスなど、電力コストが安価な地域での生産が中心となっています。

超高純度シリコンの生成プロセス

半導体用のシリコンは、わずかな不純物の混入が電気特性に大きく影響するため、極限までの高純度化が求められます。シリコンの純度レベルは「9の数」で表され、現在の主流は11N(イレブンナイン)=99.999999999%以上という超高純度です。この水準を実現するためには、いくつもの高度な精製工程を経る必要があります。

① 金属シリコンの製造(約98%)

出発点は、地中に豊富に存在する石英(SiO₂)です。これを高温の電気炉で炭素還元することで、酸素を除去し、金属状態の粗シリコンを得ます。この段階ではまだ不純物が多く含まれた工業用シリコンであり、純度は約98%程度にとどまります。

この工程は非常に電力を消費するため、シリコンはしばしば「電気の缶詰」とも呼ばれます。コスト面から、日本では電力単価が安い中国・米国・ブラジル・ロシア・フランスなどで生産が行われ、国内には輸入されるのが主流です。

② トリクロロシラン化 → 蒸留精製

次に、金属シリコンを塩酸(HCl)と反応させてトリクロロシラン(SiHCl₃)という揮発性の液体化合物に変換します。この工程は、シリコン中の不純物を取り除くための準備段階です。

得られたトリクロロシランは、蒸留によって精密に分離・精製され、不要な金属・不純物を極限まで除去します。ここで初めて、半導体グレードの高純度原料として扱えるようになります。

③ 多結晶シリコンの生成(11Nレベル)

精製されたトリクロロシランは、化学気相成長(CVD)法によって多結晶シリコンへと変換されます。反応器内に導入された水素ガスとともに加熱し、通電加熱されたシリコンロッド表面にSiが析出。棒状の多結晶シリコン(ポリシリコン)が形成されます。

この段階で得られるシリコンは、結晶構造がランダムに集まった状態ですが、純度は11Nに達します。各メーカーはさらに装置内のガス流制御や反応速度を最適化することで、より均質で高純度な製品を確保しています。

現在の多結晶シリコン市場では、中国のトンウェイ(Tongwei)やゴールデン・コンコルド、ドイツのワッカーケミー(Wacker Chemie)が上位を占めており、日本ではトクヤマが技術力で存在感を示しています。

CZ法による単結晶シリコンの生成

半導体製造において求められるのは、不純物が極限まで除去され、結晶構造が整ったシリコン素材です。その実現手段として、世界中で最も広く用いられているのがCZ法(Czochralski法/チョクラルスキー法)です。これは、多結晶シリコンから高品質な単結晶シリコンインゴットを引き上げるための代表的な技術です。

石英ルツボでの高温溶融

まず、超高純度に精製された多結晶シリコンのナゲットを、耐熱性に優れた石英製ルツボに投入します。これを電気加熱炉でおよそ1,420℃以上に加熱し、シリコンを完全に溶融状態(液体)にします。この時点で、製品の特性に応じて、微量のドーピング物質(リンやホウ素など)を添加することで、N型またはP型の導電特性をもたせます。

種結晶による結晶引き上げ

次に、予め用意した単結晶の種結晶(シードクリスタル)を、溶融シリコンの表面に接触させます。この種結晶をゆっくり回転させながら徐々に引き上げることで、種に沿った規則的な原子配列が表面から凍結・成長していきます。この過程で、不純物や欠陥を含まない均一な単結晶構造が縦方向に延伸されていき、最終的に棒状のインゴットとなります。

成長中の条件(温度勾配・引き上げ速度・回転速度)を微調整することで、結晶品質・直径・ドーピング濃度などを厳密に制御できます。1本のインゴットで、数百枚以上のシリコンウエハーが取れるため、収率も重要な設計要素です。

酸素濃度を制御するMCZ法の導入

CZ法において、シリコンが石英製ルツボと長時間接していると、酸素が溶融シリコンに溶け込むという特性があります。酸素の混入量はウエハー内の酸素濃度として影響し、最終製品の特性や信頼性に直結します。

これを高度に制御するために、近年ではMCZ法(Magnetic Czochralski)が広く用いられています。溶融シリコンに超電導磁石などで磁場をかけることで対流を抑制し、酸素拡散の制御や結晶内部の欠陥低減を実現します。特に高集積回路(LSI)や高耐圧素子においては、酸素濃度の最適化が重要な品質要素です。

インゴットからウエハーへ

こうして完成した単結晶シリコンインゴットは、直径300mm(12インチ)を標準とする大口径で成長され、ウエハー加工工程(スライス・研磨・洗浄・エッチング・ポリッシュ)を経て、半導体デバイスの土台となるシリコンウエハーへと加工されます。

1本のインゴットから生成されるウエハーは、表面平坦度±数ナノメートル、純度13N以上という精度を誇り、数千工程におよぶ微細なパターン形成にも対応できる信頼性が求められます。

N型・P型のシリコンとは?

シリコンは単体では絶縁体に近い性質を持っていますが、ごく微量の不純物を意図的に添加することで、電気を制御可能な導体へと変化させることができます。このドーピング技術によって生まれるのが、「N型」と「P型」と呼ばれる2種類のシリコン半導体です。

それぞれが異なる電荷キャリアを持ち、異なる動作原理で電流を伝導します。これらを組み合わせることで、ダイオード、トランジスタ、MOSFETといったあらゆる基本デバイスが構成されており、電子回路のすべての基礎がここにあります。

このセクションでは、N型・P型半導体の生成原理と、その電気的な振る舞いの違いについて、構造面から詳しく解説します。

N型半導体は自由電子が伝導を担う

シリコンは、そのままの状態ではすべての電子が共有結合に使われているため、自由に動ける電子(自由電子)は存在せず、絶縁体に近い性質を示します。つまり、外部から電圧をかけても電流は流れません。

しかし、この結晶構造の一部にリン(P)やヒ素(As)などの第5族元素を微量添加(ドーピング)することで状況が一変します。第5族の元素は、最外殻に5つの価電子を持っており、周囲の4つのシリコン原子と共有結合すると1つの電子が余分になります。この余った電子は、どの原子にも束縛されておらず、結晶内を自由に移動できる状態=自由電子として存在します。

電圧をかけると、この自由電子がキャリア(電流の担い手)として移動し、電流が流れるようになります。このように、負の電荷(Negative charge)を持つ自由電子が主役となる導電形態の半導体を「N型(ネガティブ型)半導体」と呼びます。

添加されるリンやヒ素は、電子を提供する役割を果たすことから「ドナー(donor)型不純物」と呼ばれます。ドナーの濃度を調整することで、導電性を高精度に制御できるため、N型シリコンはMOSFETやダイオード、CMOS回路の一部など、幅広い素子構成に利用されています。

P型半導体は正孔が電流を担う

一方で、シリコン結晶にホウ素(B)やアルミニウム(Al)など第3族の元素を添加すると、今度は電子が1つ不足した状態が生まれます。第3族の原子は価電子を3つしか持たないため、4本の共有結合のうち1本を満たせない「空席」=正孔(hole)が発生します。

この空席に近くの束縛電子が飛び込むと、その電子が元の場所を空けるため、新たな正孔が生まれます。このように、電子が玉突きのように動くことによって、正孔も結晶中を移動するように見えるのです。

正孔は正の電荷(Positive charge)を持つ仮想的な粒子として扱われ、これが電流のキャリアとなるため、このタイプの半導体を「P型(ポジティブ型)半導体」と呼びます。

添加されたホウ素のような、電子を受け取る役割の不純物は「アクセプター(acceptor)型不純物」と分類されます。P型半導体は、ダイオードの陽極側やCMOS構造のP型トランジスタ、太陽電池の電荷分離層など、負の電荷を打ち消す側の役割を持つ回路構成に多く用いられます。

N型とP型の組み合わせで機能を生む

N型・P型半導体は、それぞれ単体でも導電性を持ちますが、両者を接合することで整流・スイッチング・増幅などの基本機能が生まれることが最大のポイントです。たとえば、PN接合によってダイオードが形成され、順方向で電流を流し、逆方向で遮断するといった制御が可能になります。

このN型・P型のキャリア制御技術こそが、すべての半導体デバイスの核となる原理であり、現代の情報社会を支える最も重要な基盤技術のひとつといえるでしょう。

シリコンウエハーができるまで

高純度の単結晶シリコンインゴットが完成した後、それをそのままデバイス製造に使うわけではありません。半導体製造に必要なのは、高い平坦性と均質性を持つ薄い円盤状の素材=シリコンウエハーです。インゴットはこのウエハーに加工されるまでに、いくつもの精密な工程を経る必要があります。

- 石英製ルツボに多結晶シリコンを投入し、高温で溶融

- 微量のドーピング物質(リンやホウ素)を加え、導電特性を調整

- 種結晶(シード)を接触させ、回転しながら徐々に引き上げ

- シリコンが種結晶に従って固化し、棒状の単結晶(インゴット)が成長

まず、引き上げられたインゴットの両端(トップ部・テール部)を切断します。これらの部分は結晶構造が安定しておらず、電子デバイスの基板には適しません。続いて、残った円柱形のインゴットの外周を研削し、ウエハーサイズに合わせて正確な直径に整形(センタリング)します。

このとき、結晶方位に沿って切り欠きを入れることで、後工程での位置合わせ(アライメント)を可能にします。

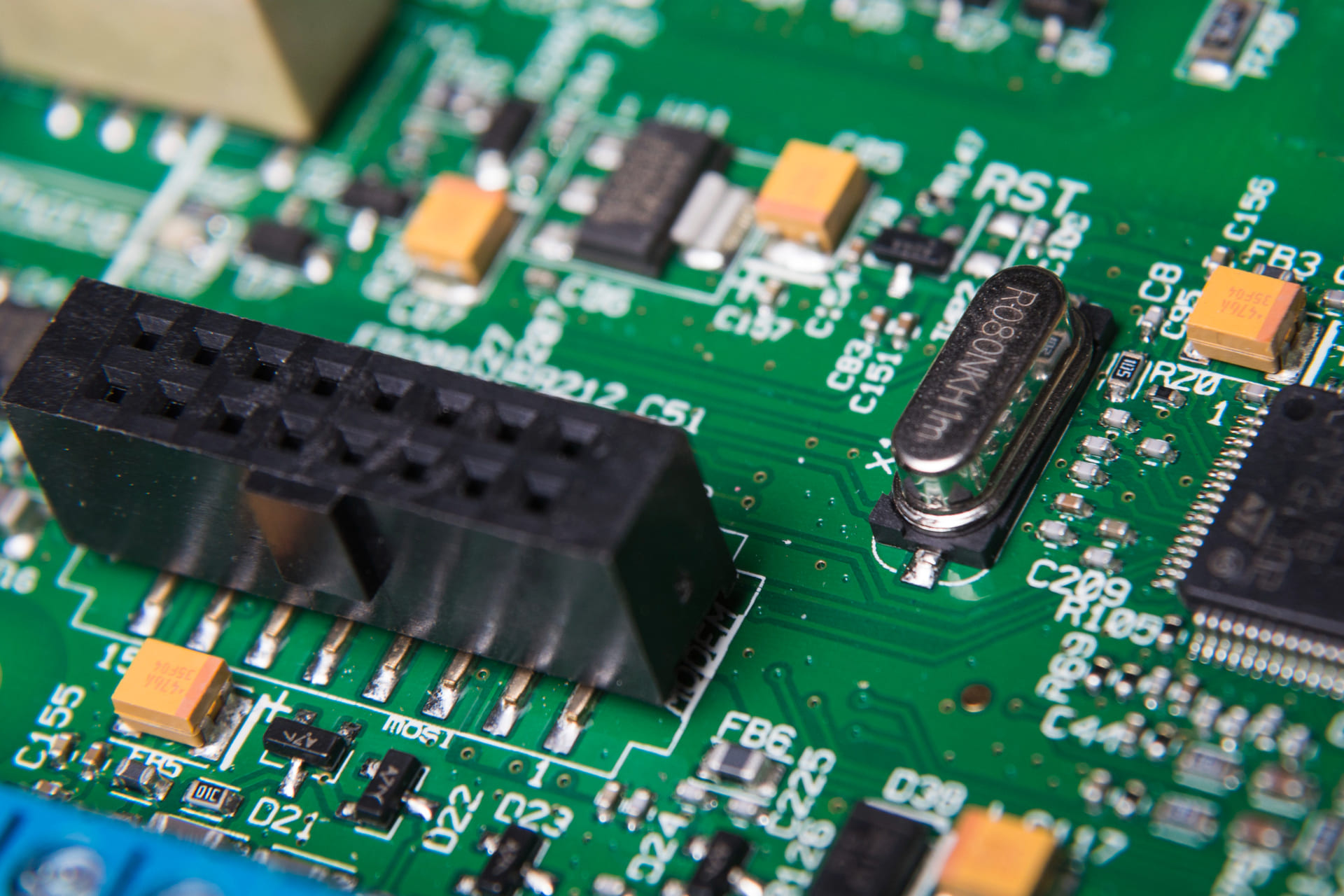

整形されたインゴットは、ワイヤーソーと呼ばれる装置によって、厚さ数百μm単位の極薄スライスに加工されます。ここでは、ダイヤモンド砥粒を含んだスラリーをワイヤーに供給しながら、微細な力で均一に切断する必要があります。

スライス中に発生する歪みや表面粗さは、後の研磨工程で除去されますが、この段階での品質管理が歩留まりや生産性に大きく影響します。

スライスされたウエハーは、表面に機械的な微細な傷(スクラッチ)や加工歪みを伴っています。これを除去し、ウエハー両面の厚み均一性(TTV)と平行度を確保するために、ラッピング(両面研磨)を行います。

続いて、化学溶液によるエッチング処理を実施。これは、研磨で生じた微細な欠陥や異物を化学的に溶解除去する工程で、デバイス製造に支障をきたす表面欠陥の発生を防ぎます。

最後に行うのが、ポリシング(鏡面研磨)です。この工程では、ナノレベルのスラリーを用いて表面の凹凸を原子レベルで平滑化し、光を完全に反射する鏡面状態に仕上げます。これにより、次工程であるフォトリソグラフィ工程におけるパターンの精密な描画が可能になります。

要求されるウエハーの平坦性は極めて高く、東京ドームをウエハーサイズに拡大した場合でも、高低差はわずか20μm以内という驚異的な精度です。

ウエハーの品質水準

このようにして完成したシリコンウエハーは、純度13N(99.999999999999%)という驚異的なレベルを持ち、直径200〜300mmの大口径にわたって均一な厚み、低歪み、高平滑性が確保されています。

これにより、ナノレベルの微細配線やトランジスタ構造の形成が可能となり、LSIやCPU、メモリ、パワーデバイスといったあらゆる電子部品のベース材料として供給されます。

シリコンウエハーは単なる素材ではなく、最先端加工技術の結晶ともいえる存在であり、その品質がデバイス性能と信頼性を大きく左右します。

ウエハーの大口径化と今後

半導体製造におけるコスト競争力と生産効率の向上を実現するうえで、ウエハーの大口径化は長年にわたり重要なテーマとして取り組まれてきました。ウエハーの直径が大きくなることで、1枚あたりに形成できるチップ数が増加し、単位コストの低減につながるという明確なメリットがあるためです。

現在、量産の主流は12インチ(300mm)ウエハーですが、各国の大手半導体メーカーや装置ベンダーの間では、次世代規格である16インチ(450mm)ウエハーの導入可能性が再び注目されています。

ウエハーの面積は直径の2乗に比例して増加するため、300mmから450mmへと拡大すれば、理論上、約2.25倍のチップを1枚から取り出せることになります。これにより、製造ラインのスループットが向上し、ラインあたりのチップ供給量が飛躍的に増加します。

また、大口径ウエハーでは装置の停止頻度や段取り替えの回数が減り、工程あたりのコスト効率が改善されるといった副次的な効果も見込まれます。

| 課題項目 | 説明 | 主な影響領域 |

|---|---|---|

| 装置対応の再設計コスト | リソグラフィー、エッチング、CVDなど主要な前工程装置すべてにおいて450mm対応の設計変更が必要となり、膨大な初期投資が発生 | 製造設備投資、装置メーカーとの連携、導入判断の遅延 |

| 搬送・取り扱いの困難性 | ウエハーの大型化に伴い、重量や取り回しが増加。自動搬送システムやFOUP、カセットなど搬送機構の刷新が求められる | クリーンルーム設計、搬送設備、ロジスティクス全般 |

| 機械的歪みと平坦度確保の難易度 | 大口径ウエハーでは厚みの均一化や面内平坦性の制御が難しくなり、微細プロセスでの歩留まり低下のリスクが高まる | 歩留まり、生産安定性、最終製品の信頼性 |

| 需要予測と供給体制のズレ | 市場の急変動リスクに対し、大量生産を前提とした450mm導入の採算性が読みづらく、設備投資判断を鈍らせる要因となる | 生産計画、設備稼働率、ファウンドリー戦略全体 |

450mm化の動向と業界連携の必要性

一時は沈静化していた450mm化の議論も、近年のAI需要・先端半導体の爆発的成長・地政学的な生産シフトを背景に、再び現実味を帯びつつあります。欧州・米国・アジアの複数企業が、共同コンソーシアムや次世代投資枠を通じて研究開発を再開しており、装置メーカー側でも試験機やプロトタイプの開発が進んでいます。

とはいえ、実用化には設計・材料・製造・検査・搬送・パッケージングまでを網羅した業界全体の垂直統合と標準化が不可欠です。単独のプレイヤーだけで推進できる規模ではなく、エコシステム全体での中長期的な協調がカギとなるでしょう。

まとめ

シリコンは、ただ豊富に存在するというだけでなく、加工性・電気特性・構造安定性のすべてを高いレベルで兼ね備えた「理想的な半導体材料」です。石英を起点とした高純度化プロセス、CZ法による単結晶生成、ウエハーへの加工まで、精緻に管理された工程によって、半導体製造の基盤が支えられています。

また、ドーピングによるN型・P型制御を通じて、シリコンは自由自在にその電気特性をカスタマイズでき、トランジスタやダイオードといった高機能素子の構成要素となります。ウエハーの大口径化も進み、生産性と歩留まりの最適化に貢献し続けています。

シリコンという素材を正しく理解することは、今後ますます高度化するデバイス開発や電子産業全体の競争力強化にとって、欠かせない一歩となるでしょう。